# МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

Государственное образовательное учреждение высшего профессионального образования

«Оренбургский государственный университет»

Кафедра проектирования и технологии радиоэлектронных средств

В.В. ИЗВОЗЧИКОВА, Е.А. КОРНЕВ

# ЦИФРОВАЯ СХЕМОТЕХНИКА

МЕТОДИЧЕСКИЕ УКАЗАНИЯ К ЛАБОРАТОРНОМУ ПРАКТИКУМУ

Рекомендовано к изданию Редакционно-издательским советом государственного образовательного учреждения высшего профессионального образования «Оренбургский государственный университет»

ББК 32.852 я7 Б 91 УДК 621.215 (07)

Рецензент кандидат технических наук, доцент А.В. Хлуденев

Извозчикова В.В., Корнев Е.А. Б 91 Цифровая схемотехника: Методические указания к лабораторному практикуму. - Оренбург: ГОУ ОГУ, 2005. - 32c.

Лабораторный практикум состоит из 6 лабораторных работ по изучению принципов построения и функционирования логических элементов, устройств комбинационного и последовательностного типов и готовых интегральных микросхем малой и средней степени интеграции с использованием программы **Electonics WorkBench** (EWB).

Каждая работа включает теоретическое изложение материала, методику выполнения, контрольные вопросы и задания.

Методические указания предназначены для выполнения лабораторного практикума по дисциплине "Схемотехника" специальности 230101.

ББК 32.852 я7

<sup>©</sup> Извозчикова В.В., 2005

<sup>©</sup> ГОУ ОГУ, 2005

## Введение

Целью данных методических указаний является практическое изучение принципов построения и функционирования логических элементов, устройств комбинационного и последовательностного типов и готовых интегральных микросхем малой и средней степени интеграции с использованием программы **Electonics WorkBench (EWB)**.

Разработка любого электронного устройства сопровождается физическим или математическим моделированием. Физическое моделирование связано с большими материальными затратами, поскольку требует изготовление макетов и трудоёмкое исследование, Часто физическое моделирование ИХ невозможно из-за чрезвычайной сложности устройства, например, при разработки больших и сверхбольших интегральных микросхем. В этом случае прибегают к математическому моделированию использованием c средств И вычислительной техники.

EWB позволяет строить и анализировать любые электронные схемы, включающие в свой состав любые цифровые устройства от самых простых до сложных.

Особенностью программы является наличие контрольно-измерительных приборов, по внешнему виду и характеристикам приближенных к их промышленным аналогам.

Программа легко осваивается и достаточно удобна в работе.

# 1 Система моделирования Elektronics Workbench

История создания программы Elektronics Workbench (EWB) начинается с 1989 г. Ранние версии программы состояли из двух независимых частей. С помощью одной половины программы можно было моделировать аналоговые устройства, с помощью другой - цифровые. Такое "раздвоенное" состояние создавало определенные неудобства, особенно при моделировании смешанных аналого-цифровых устройств. В 1996г. в версии 4.1 эти части были объединены и через полгода выпущена пятая версия программы. Она дополнена средствами анализа примерно в объеме программы Micro-Cap V, переработана и несколько расширена библиотека компонентов. Средства анализа цепей выполнены в типичном для всей программы ключей - минимум усилий со стороны пользователя. Дальнейшим развитием EWB является программа EWB Layout, предназначенная для разработки печатных плат. Программа EWB обладает преемственностью снизу вверх, т.е. все схемы созданные в версиях 3.0 и 4.1, могут быть промоделированы в версии 5.0. Следует отметить, что EWB позволяет также моделировать устройства, для которых задание на моделирование подготовлено в текстовом формате SPICE, обеспечивая совместимость с программами Micro-Cap и Pspice.

Программа EWB 4.1 рассчитана для работы в среде Windows 3.хх или 95/98 и занимает около 5 Мбайт дисковой памяти, EWB 5.0 - в среде Windows 95/98 и NT 3.51, требуемый объем дисковой памяти - около 16 Мбайт. Для размещения временных файлов требуется дополнительно 10-20 Мбайт свободного пространства.

#### 1.1 Система меню

#### **1.1.1 Меню File**

Меню File предназначено для загрузки и записи файлов, получение твердой копии выбранных для печати составных частей схемы, а также для импорта/экспорта файлов в форматах других систем моделирования и программ разработки печатных плат.

Первые четыре команды этого меню: New (Ctrl+N), Open (Ctrl+O), Save (Ctrl+S), Save As... - типичные для Windows команды работы с файлами и по этому пояснения не требуют. Для этих команд в пятой версии имеются иконки со стандартным изображением. Остальные команды имеют следующее назначение:

- Revent to Savent... стирание всех изменений, внесенных в текущем сеансе редактирования, и восстановление схемы в первоначальном виде;

- Print... (Ctrl+P) выбор данных для вывода на принтер;

- Print Setup... настройка принтера;

- Exit (Alt+F4) выход из программы;

- Install... установка дополнительных программ.

#### 1.1.2 Меню Edit

Меню Edit позволяет выполнять команды редактирования схем и копирование экрана.

Назначение команд:

- Cut (Ctrl+X) стирание (вырезание) выделенной части схемы с сохранением ее в буфере обмена (Clipboard). Выделенные компоненты окрашиваются в красный цвет;

- Copy (Ctrl+C) копирование выделенной части схемы в буфер обмена;

- Paste (Ctrl+V) вставка содержимого буфера обмена на рабочее поле программы;

- Delete (Del) стирание выделенной части схемы;

- Select All (Ctrl+A) выделение всей схемы;

- Copybits (Ctrl+I) команда превращения курсора мыши в крестик, которым по правилу прямоугольника можно выделить нужную часть экрана, после отпускания левой кнопки мыши выделенная часть копируется в буфер обмена, после чего его содержимое может быть импортировано в любое приложение Windows. Копирование всего экрана производится нажатием клавиши Print Screen: копирование активной в данный момент части экрана, например, диалогового окна комбинацией Alt + Print Screen. Команда очень удобна при подготовке отчетов по моделированию, например, при оформлении лабораторных работ;

- Show Clipboard показать содержимое буфера обмена.

#### 1.1.3 Меню Сігсиіт

Меню Circuit используется для подготовки схем, а также для задания параметров моделирования.

Назначение команд:

- Activate (Ctrl+G) запуск моделирования;

- Stop (Ctrl+T) остановка моделирования;

- Pause (F9) прерывание моделирования;

- Label... (Ctrl+L) ввод позиционного обозначения выделенного компонента (например, R1 для резистора, C5 для конденсатора и т.д.);

- Value... (Ctrl+U) изменение номинального значения параметра компонента; команда выполняется также двойным щелчком по компоненту;

- Model... (Ctrl+M) выбор модели компонента; команда выполняется также двойным щелчком по компоненту;

- Zoom (Ctrl+Z) развертывание выделенной подсхемы;

- Rotate (Ctrl+R) вращение выделенного компонента; большинство компонентов поворачиваются против часовой стрелки на 90° при каждом выполнении команды, для измерительных приборов (амперметр, вольтметр и др.) меняются местами клеммы подключения. Команда чаще всего используется при подготовке схем. В готовой схеме пользоваться командой нецелесообразно, поскольку это чаще всего приводит к путанице в таком случае компонент нужно сначала отключить от подсоединенных цепей, а затем вращать;

- -Fault (Ctrl+F) имитация неисправности выделенного компонента путем введения:

- 1) Leakage сопротивления утечки;

- 2) Short короткого замыкания;

- 3) Ореп обрыва;

- 4) None неисправность отсутствует ( включено по умолчанию);

- Subcircuit... (Ctrl+B) преобразование предварительно выделенной части схемы в подсхему. Выделенная часть схемы должна быть расположена таким образом, чтобы в выделенною область не попали не относящиеся к ней проводники и компоненты;

- Wire Color... изменение цвета предварительно выбранного проводника. Более простой способ выполнения команды двойной щелчок мышью на проводнике, после чего в меню выбирается один из шести предлагаемых цветов. Необходимость расцветки особенно важна для проводников, соединяющих контрольные точки (узлы) схемы с осциллографом или логическим анализатором в этом случае цвет проводника определяет цвет осциллограммы;

- Preferences... (Ctrl+ E) выбор элементов оформления схемы;

- Show grid показать сетку для удобства рисования схемы (по умолчанию эта опция выключена, остальные включены). Опция активна только при включенной опции Use grid (использовать сетку);

- Show labels показать позиционные обозначения компонентов, например, C1, C2 для конденсаторов;

- Show models показать имена моделей компонентов, например, типов транзисторов;

- Show values показать номиналы компонентов, например, сопротивления резисторов.

#### 1.1.4 Меню Window

Меню Window содержит следующие команды:

- Arrange (CTRL+W) упорядочивание информации в рабочем окне EWB путем перезаписи экрана, при этом исправляются искажения изображений компонентов и соединительных проводников;

- Circuit вывод схемы на передний план;

- Description (CTRL+D) вывод на передний план описания схемы, если оно имеется, или окно-ярлык для его подготовки (только на английском языке).

## 1.1.5 Меню НеІр

Меню Help построено стандартным для Windows способом. Оно содержит краткие сведения по всем рассмотренным выше командам, библиотечным компонентам и измерительным приборам, а также сведения о самой программе. Отметим, что для получения справки по библиотечному компоненту его необходимо отметить на схеме щелчком мыши (он высветится красным цветом) и затем нажать клавишу F1.

## 1.1.6 Меню Analysis

Первые три команды - Activate (CTRL+G), Stop (CTRL+T), Pause (F9) - аналогичны командам меню Circuit программы EWB 4.1.

Назначение остальных команд следующее:

- Analysis Options... (CTRL+Y) набор команд для установки параметров моделирования;

- -Global настройки общего характера, задаются с помощью диалогового окна, в котором параметры имеют следующее назначение:

- 1) ABSTOL -абсолютная ошибка расчета токов;

- 2) GMIN минимальная проводимость ветви цепи (проводимость ветви, меньшая GMIN, считается равной нулю);

- 3) PIVREL, PIVTOL относительная и абсолютная величины элемента строки матрицы узловых проводимостей (например, при расчете по методу узловых потенциалов), необходимые для его выделения в качестве ведущего элемента;

- 4) RELTOL допустимая относительная ошибка расчета напряжений и токов;

- 5) ТЕМР температура, при которой проводится моделирование;

- 6) VNTOL допустимая ошибка расчета напряжений в режиме Transient (анализ переходных процессов);

- 7) CHGTOL допустимая ошибка расчета зарядов;

- 8) RAMPTIME начальная точка отсчета времени при анализе переходных процессов;

- 9) CONVSTEP относительный размер шага интеграции при расчете режима по постоянному току;

- 10) CONVABSSTEP абсолютный размер шага интеграции при расчете режима по постоянному току;

- 11) CONVLIMIT включение или выключение дополнительных средств для обеспечения сходимости интеграционного процесса (например, за счет использования метода вариации напряжений источников питания);

- 12) RSHUNT допустимое сопротивление утечки для всех узлов относительно общей шины (заземления);

- DC настройка для расчета режима по постоянному току (статистический режим). Для настройки этого режима используется диалоговое окно, параметры которого имеют следующее назначение:

- 1) ITL1 максимальное количество итераций приближенных расчетов;

- 2) GMINSTEPS размер приращения проводимости в процентах от GMIN (используется при слабой сходимости итерационного процесса);

- 3) SRCSTEPS размер приращения напряжения питания в процентах от его номинального значения при вариации напряжения питания (используется при слабой сходимости итерационного процесса).

- Transient настройки параметров режима анализа переходных процессов:

- 1) ITL4 максимальное количество итераций за время анализа переходных процессов;

- 2) MAXORD максимальный порядок (от 2 до 6) метода интегрирования дифференциального уравнения;

- 3) TRTOL допуск на погрешность вычисления переменной;

- 4) METHOD метод приближенного интегрирования дифференциального уравнения;

- 5) TRAPEZOIDAL метод трапеций,

- 6) GEAR метод Гира;

- 7) АССТ разрешение на вывод статистических сообщений о процессе моделирования;

- Device выбор параметров МОП-транзисторов:

- 1) DEFAD площадь диффузионной области стока,  $M^2$ ;

- 2) DEFAS площадь диффузионной области истока,  $M^2$ ;

- 3) DEFL длина канала полевого транзистора, м;

- 4) DEFW ширина канала, м;

- 5) TNOM номинальная температура компонента;

- 6) BYPASS включение или выключение нелинейной части модели компонента;

- 7) TRYTOCOMPACT включение или выключение линейной части модели компонента.

# 2 Контрольно-измерительные приборы

Панель контрольно-измерительных приборов находится под полем меню рабочего окна и содержит цифровой мультиметр, функциональный генератор, двухканальный осциллограф, измеритель амплитудно-частотных и фазочастотных характеристик, генератор слов (кодовый генератор), 8-канальный логический анализатор и логический преобразователь. Вид панели контрольно-измерительных приборов показан на рисунке 2.1. Общий порядок работы с приборами такой: иконка прибора курсором переносится на рабочее поле и подключается проводниками к исследуемой схеме. Для приведения прибора в рабочее (развернутое) состояние необходимо дважды щелкнуть курсором по его иконке

Рисунок 2.1 - Панель контрольно-измерительных приборов

## 2.1 Мультиметр

Лицевая панель мультиметра показана на рисунке 2.2. На лицевой панели мультиметра расположен дисплей для отображения результатов измерения, клеммы для подключения к схеме и кнопки управления.

Ammeter resistance – внутреннее сопротивление вольтметра.

Voltmeter resistance – входное сопротивление вольтметра.

Ohmmeter current – ток через контролируемый объект;

Decibel standard – установка эталонного напряжения при измерении ослабления или усиления в децибелах.

Рисунок 2.2 - Лицевая панель мультиметра

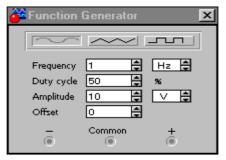

# 2.2 Функциональный генератор

Лицевая панель генератора показана на рисунке 2.3. Управление генератора осуществляется следующими органами управления:

- выбор формы выходного сигнала: синусоидальной (выбрана по умолчанию), треугольной и прямоугольной; s

- - Amplitude 10 🗦 🗸 установка амплитуды выходного сигнала;

Рисунок 2.3 - Лицевая панель функционального генератора

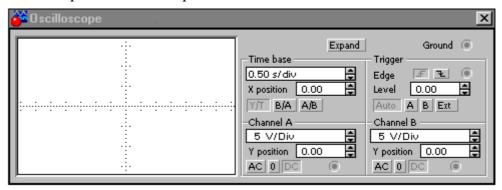

## 2.3 Осциллограф

Лицевая панель осциллографа показана на рисунке 2.4. Осциллограф имеет два канала (CHANNEL) А и В с раздельной регулировкой чувствительности в диапазоне от 10 мкВ/дел (mV/Div) до 5 кВ/дел (kV/Div) и регулировкой смещения по вертикали (Y POS). Выбор режима по входу осуществляется нажатием кнопок тока (его еще называют режимом "закрытого входа"). В режиме 0 входной зажим замыкается на землю. В режиме DC (включён по умолчанию) можно проводить осциллографические измерения как постоянного так и переменного тока. Этот режим еще называют режимом "открытого входа".

Рисунок 2.4 - Лицевая панель осциллографа

Режим развертки выбирается кнопками Y/T, B/A и A/B. В режиме Y/T (обычный режим, включен по умолчанию) реализуются следующие режимы развертки; по вертикали — напряжение сигнала, по горизонтали — время; в режиме B/A: по вертикали — сигнал канала B, по горизонтали — сигнал канала A; в режиме A/B: по вертикали — сигнал канала A, по горизонтали — сигнал канала B.

В режиме развертки Y/T длительность развертки (TIME BASE) может быть задана в диапазоне от 0,1 нс/дел до 1 с/дел с возможностью установки смещения в тех же единицах по горизонтали, т.е. по оси X.

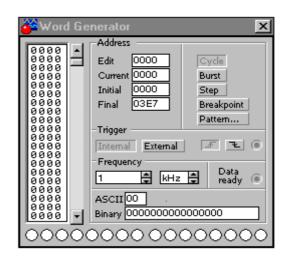

## 2.4 Генератор слова

Внешний вид генератора слова в развернутом виде показан на рисунке 2.5. Генератор (его называют еще кодовым генератором) предназначен для генерации шестнадцати 8-разрядных двоичных слов, которые набираются пользователем на экране, расположенном в левой части лицевой панели. Для набора двоичных комбинаций необходимо щелкнуть мышью на соответствующем разряде и затем ввести с клавиатуры 0 или 1. Дальнейшие перемещения по полю экрана удобнее проводить не с помощью мыши, а клавишами управления курсором.

Рисунок 2.5 - Лицевая панель генератора слова

Сформированные слова выдаются на восемь расположенных в нижней части прибора выходных клемм-индикаторов:

С индикацией выходного сигнала в двоичном коде на клеммах индикаторов и в окне Binary; В пошаговом режиме (при нажатии кнопки STEP на панели), циклическом (при нажатии кнопки CYCLE на панели) или с выбранного слова до конца (при нажатии кнопки BURST) при заданной частоте посылок (установка – нажатиями кнопок в окне FREQUENCY); При внутреннем (при нажатии кнопки INTERNAL) или внешнем сигнале синхронизации (при нажатии кнопки EXTERNAL);

Запуск по переднему или заднему фронту задается используя кнопки

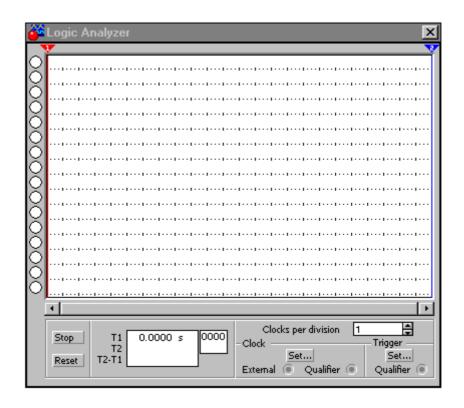

# 2.5 Логический анализатор

Внешний вид логического анализатора показан на рисунке 2.6. Анализатор предназначен для отображения на экране монитора 8-разрядных кодовых последовательностей одновременно в восьми точках схемы, а также в виде двоичных чисел на входных клеммах-индикаторах и в виде шестнадцатеричных чисел в окне HEX. При нажатии кнопки CLEAR информация на экране стирается.

Рисунок 2.6 - Лицевая панель логического анализатора

В блоке TRIGGER расположены кнопки запуска по положительному (включена по умолчанию) или отрицательному спаду сигнала и клемма для подключения вешнего источника синхронизации, например, генератора слова (подключается после нажатия кнопки EXTERNAL). Кроме того, предусмотрен автозапуск и запуск по заданной двоичной комбинации (после нажатия кнопки PATTERN на панели прибора), устанавливаемой пользователем в появившемся окошке, путем ведения туда с клавиатуры 1, 0 или X (неопределенное состояние), предварительно щелкнув мышью на нужном разряде.

# 2.6 Логический преобразователь

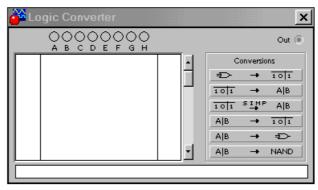

Внешний вид логического преобразователя показан на рисунке 2.7.

На панели преобразователя показаны клеммы-индикаторы входов А, В,....., Н и одного выхода ОUТ, экран для отображения таблицы истинности исследуемой схемы, экранная строка для отображения ее булева выражения (в нижней части). В правой части панели расположены кнопки управления процессом преобразования. Возможные варианты использования преобразователя:

- а) логический анализатор n-входового устройства с одним выходом (входы исследуемого устройства подключаются к клеммам А...Н, а выход к клемме OUT). В этом случае используя кнопки управления, получим:

- 1) таблицу истинности исследуемого устройства;

- 2)  $\rightarrow$  A|B булево выражение, реализуемое устройством;

- 3) торт втир АІВ минимизированное булево выражение;

- 4) АВ Схему устройства на логических элементах без ограничения их типа;

- 5) A NAND схему устройства только на логических элементах И-НЕ.

- б) синтез логического устройства по таблице истинности.

Щелчком мыши по входным клеммам A,B,...H, начиная с клеммы A, активизируем мышью требуемое число входов анализатора, в результате чего на экране анализатора получим начальную таблицу истинности, в которой будут представлены все возможные комбинации входных сигналов.

Отредактируем полученную таблицу в соответствии с заданием путем записи 1,0 или X в столбце OUT в строках, которые по комбинации входных сигналов соответствуют заданным;

в) синтез логического устройства по булевому выражению.

Булево выражение заноситься в экран-строку. Используются символы A...H, при инверсии  $A^*...H^*$ . Нажимая кнопку  $A^{|B|} \rightarrow \overline{IO|I}$ , получаем таблицу истинности.

Рисунок 2.7 - Лицевая панель логического преобразователя

# 3 Моделирование и анализ работы цифровых устройств

Целью лабораторных работ, предлагаемых в данном методическом указании, является моделирование цифровых устройств, начиная от простейших логических элементов до сложных многофункциональных узлов, применяемых в той или иной комбинации в вычислительной технике, автоматике, информационно-измерительной технике и в других областях прикладной радиоэлектроники.

## 3.1 Лабораторная работа №1

Цель работы: Исследование и синтез логических элементов и устройств на их основе.

#### 3.1.1 Логические элементы

Известно, что математической основой цифровых вычислительных устройств является двоичная арифметика, в которой используются всего два числа — 0 и 1. Выбор двоичной системы счисления диктовался требованиями простоты технической реализации самых сложных задач с использованием всего одного базового элемента - ключа, который имеет два состояния: включен (замкнут) или выключен (разомкнут). В цифровой технике практические аналоги такого ключа принято называть логическими элементами. При этом в зависимости от выполняемых функций каждый элемент имеет свое название и соответствующее графическое обозначение. На рисунке 3.1 показаны обозначения базовых логических элементов, принятые в программе EWB 4.1.

Рисунок 3.1 - Графические обозначения буферного логического элемента, элементов И (AND), ИЛИ (OR). Исключающее ИЛИ (XOR) и их инверсные варианты во втором ряду (NOT, NAND, NOR, XNOR соответственно)

## 3.1.2 Логический элемент с тремя состояниями

логического элемента  $\mathbf{c}$ тремя состояниями несколько модифицирована с учетом возможностей программы EWB. За основу взят базовый элемент серии 134 и к нему добавлен элемент, обеспечивающий возможность реализации режима третьего состояния или так называемого Zсостояния. Следует отметить, что рассматриваемый элемент является важным компонентом многих цифровых ИМС, начиная от простейших логических элементов (например, К155ЛА9) и кончая сложными регистрами и шинными формирователями, обеспечивающими возможность реализации наиболее

распространенных архитектур ЭВМ и микропроцессорных систем управления с общей шиной.

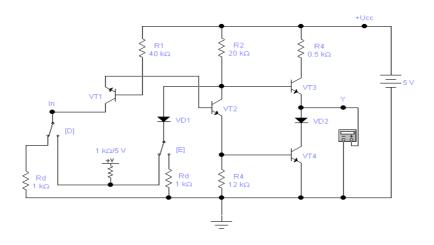

Принципиальная схема логического элемента с тремя состояниями представлена на рисунке 3.2. Она содержит базовый логический элемент серии 134 на транзисторах VT1 ... VT 4, резисторах R1...R4 и диоде VD2. В базовом элементе в качестве VT1 используется так называемый многоэмиттерный транзистор, однако ввиду отсутствия такового в библиотеке EWB он представлен обычным транзистором. Ко входу In логического элемента подключен имитатор входного сигнала на переключателе D, управляемый с клавиатуры клавишей D, резистора Rd, имитирующего выходное сопротивление источника логического нуля, и источника напряжения V=+5 B с внутренним сопротивлением 1 кОм, имитирующего источник входного сигнала в режиме генерации логической единицы. К точке A схемы подключены диод VD1 и имитатор источника управления состоянием выхода логического элемента на переключателе Е, управляемого клавишей Е. Все элементы дополнительной схемы компоненты из библиотек Passive и Control. В исходном состоянии диод VD1 напряжением положительной полярности на его катоде и он не оказывает влияния на работу схемы. К эмиттеру транзистора VT1 подключен резистор Rd, на котором создается падение напряжения

$$Uin=Rd(Ucc-Ube)/(R1+Rd), (3.1)$$

где Ucc=5 В – напряжение питания;

Ube=0,7 В – напряжение база-эмиттер открытого транзистора.

При

$$Uin < 0.4B$$

(3.2)

логический элемент воспринимает входной сигнал как сигнал логического нуля. При этом напряжение на коллекторе транзистора VT1 и базе VT2 недостаточно для открывания последнего. В результате падение напряжения на резисторе R3 близко к нулю и транзистор VT4 будет закрыт, а база транзистора VT3 соединена с источником питания Ucc через резистор R2 и VT3 будет открыт. При этом выходное напряжение Uy, измеряемое мультиметром, примерно равно

$$Uy = (Ucc - U_{KB HAC} - U_{\Pi P})Ry/(Ry + R4),$$

(3.3)

где  $U_{\text{KБ HAC}} < 1$  B — напряжение насыщения транзистора VT4;

$U_{\Pi P}$  <1 B – падение напряжения на диоде VD2;

Ry – сопротивление нагрузки, равное в данном случае входному сопротивлению мультиметра.

Если выбрать Ry»R4, то Uy>3 B, т.е. при подаче на вход сигнала логического нуля на выходе получим сигнал логической единицы. Таким образом, схема на рисунке 3.2 является логическим элементом НЕ (инвертором).

Рисунок 3.2 - Логический элемент с тремя состояниями

При переводе клавишей D одноименного переключателя в другое положение на эмиттер транзистора VT1 подается сигнал логической единицы, в результате чего эмиттерный переход закрывается, и транзистор VT1 переводится в инверсный режим. В этом случае под действием тока, протекающего по цепи база-коллектор VT1, транзистор VT2 открывается и за счет падения напряжения на резисторах R2, R3 транзистор VT3 закроется, а VT4 – откроется, и на выходе У установится сигнал логического нуля.

При переводе клавишей Е одноименного переключателя во второе положение напряжение коллектора транзистора VT2 (точка A) будет равно

$$U_a = U_{\Pi P} + (Ucc - U_{\Pi P})Rd/(Rd + R2),$$

(3.4)

При выполнении неравенства R2»Rd напряжение  $U_{\Pi P}$  <1B, что недостаточно для открытия двух переходов (эмиттерного и диодного), и транзистор VT3 будет закрыт вне зависимости от состояния транзистора VT2. Если этот транзистор открыт (наихудший случай), то с учетом его напряжения насыщения, сравнимого с  $U_{\Pi P}$  падение напряжения на резисторе R3 будет ничтожно малым, следовательно, транзистор VT4 будет закрыт. Таким образом, выход схемы полностью отключается от нагрузки, что может быть зафиксировано мультиметром в режиме омметра — он будет измерять очень большое сопротивление.

Кроме демонстрации рассмотренных режимов схемы, она может быть использована также для исследования:

- помехоустойчивости по основному входу и входу разрешения третьего состояния путем варьирования сопротивления Rd с учетом выражений (3.1), (3.2) и (3.4):

- влияния сопротивления нагрузки на амплитуду выходного напряжения вентиля при формировании сигнала логической единицы путем изменения входного сопротивления мультиметра с учетом выражения (3.3).

- влияния сопротивления нагрузки, подключенной между выходом и шиной питания Ucc, на выходное напряжение вентиля при формировании сигнала логического нуля.

- влияния емкостной нагрузки на форму и амплитуду выходного сигнала вентиля.

## 3.1.3 Контрольные вопросы и задания

- 3.1.3.1 Какими свойствами обладает логический элемент с тремя состояниями, какие задачи цифровой техники он позволил решить?

- 3.1.3.2 Проведите исследования логического элемента на рисунке 3.2.

- 3.1.3.3 Синтезировать на ТТЛ логике элементы: ИЛИ-НЕ, инвертор, И-НЕ с сложным инвертором.

- 3.1.3.4 Синтезировать элемент НЕ на МДП в положительной и отрицательной логике.

- 3.1.3.5 Синтезировать на МДП логике элементы: ИЛИ-НЕ, И-НЕ, ИЛИ, И.

- 3.1.3.6 Синтезировать на КМДП логике элементы: ИЛИ-НЕ, И-НЕ.

- 3.1.3.7 Случайным образом сформировать 40 значений таблицы истинности логической функции 6 переменных.

- 3.1.3.8 Реализовать функцию из 7 задания логических элементах в базисе И-HE.

- 3.1.3.9 Реализовать функцию из 7 задания на логических элементах в базисе ИЛИ-НЕ.

## 3.2 Лабораторная работа №2

Цель работы: Исследование и синтез устройств комбинационного типа

## 3.2.1 Мультиплексоры и демультиплексоры

Назначение мультиплексоров — коммутировать в заданном порядке сигналы, поступающие с нескольких входных шин на одну выходную. У мультиплексора может быть, например, 16 входов и один выход. Для выбора любого из 16 каналов необходимо иметь 4 входа селекции ( $2^4 = 16$ ), на которые подается двоичный адрес канала. Так, для передачи данных от канала номер 9 на входах селекции необходимо установить код 1001. В силу этого мультиплексоры часто называют селекторами или селекторами-мультиплексорами.

Мультиплексоры применяются, например, в МП 18088 для выдачи на одни и те же выводы МП адреса и данных, что позволяет существенно сократить общее количество выводов микросхемы; в микропроцессорных системах управления мультиплексоры устанавливают на удаленных объектах для возможности передачи информации по одной линии от нескольких установленных на них датчиков.

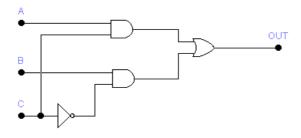

На рисунке 3.3 приведена схема двухканального мультиплексора, состоящего из элементов ИЛИ, НЕ и двух элементов И.

Рисунок 3.3 - Схема двухканального мультиплексора

Результаты моделирования двухканального мультиплексора, показывают, что его выходной сигнал описывается булевым выражением OUT=BC'+AC, т.е. сигнал из канала A проходит на выход при адресном входе C=0, а из канала B- при C=1, что и соответствует логике работы мультиплексора.

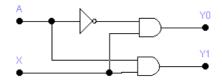

Демультиплексоры в функциональном отношении противоположны мультиплексорам. С их помощью сигналы с одного информационного входа распределяются в требуемой последовательности по нескольким выходам. Выбор нужной выходной шины, как в мультиплексоре, обеспечивается установкой соответствующего кода на адресных входах. При m адресных входах демультиплексор может иметь до  $2^m$  выходов.

Принцип работы демультиплексора поясним с помощью схемы на рисунке 3.4, на котором обозначено: X – информационный вход, A – вход адреса, YO, Y1 – выходы. Схема содержит два элемента U и один элемент HE. U3 рисунка 3.18 нетрудно видеть, что при A=0 сигнал информационного входа передается на выход Y0, а при A=1 на выход Y1

Рисунок 3.4 - Схема демультиплексора

## 3.2.2 Шифраторы и дешифраторы

Шифраторы (кодеры) используются чаще всего для преобразования десятичных чисел в двоичный или двоично-десятичный код, например, в микрокалькуляторах, в которых нажатие десятичной клавиши соответствует генерации соответствующего двоичного кода. Поскольку возможно нажатие сразу нескольких клавиш, в шифраторах используется принцип приоритета старшего разряда.

Дешифратор (декодер) – устройство с несколькими входами и выходами, у которого определенным комбинациям входных сигналов соответствует активное со стояние одного из выходов, т.е. дешифратор является обращенным по входам демультиплексором, у которого адресные входы стали информационными, а бывший информационный вход стал входом разрешения. Поэтому часто дешифраторы называют дешифраторами-демультиплексорами и наоборот.

Дешифраторы и демультиплексоры в виде серийных ИМС средней степени интеграции широко используются в информационно-измерительной технике и микропроцессорных системах управления, в частности, в качестве коммутаторов распределителей информационных сигналов и синхроимпульсов, для демультиплексирования данных и адресной логики в запоминающих устройствах, а также для преобразования двоично-десятичного кода в десятичный с целью управления индикаторными и печатающими устройствами.

Дешифраторы как самостоятельные изделия электронной техники имеют 4, 8 или 16 выходов. Если требуется большее число выходов, дешифраторы наращиваются в систему.

## 3.2.3 Цифровой компаратор

Цифровые компараторы (от английского compare — сравнивать) выполняют сравнение двух чисел A, B одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. B зависимости от схемного исполнения компараторы могут определять равенство A == B или неравенства A < B, A > B. Результат сравнения отображается в виде логического сигнала на одноименных выходах.

Цифровые компараторы применяются для выявления нужного числа в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах, а также в адресных селекторах.

## 3.2.4 Устройство контроля четности

Операция контроля четности двоичных чисел позволяет повысить надежность передачи и обработки информации. Ее сущность заключается в суммировании по модулю 2 всех разрядов с целью выяснения четности числа, что позволяет выявить наиболее вероятную ошибку в одном из разрядов двоичной последовательности. Например, если при передаче кода 1001 произойдет сбой во втором разряде, то на приемном пункте получим код 1101 — такую ошибку определить в общем случае затруднительно. Если же код относится к двоичнодесятичному (8-4-2-1), то ошибку легко обнаружить, поскольку полученный код (десятичный эквивалент — число 13) не может в принципе принадлежать к двоично-десятичному.

Обнаружение ошибок путем введения дополнительного бита четности происходит следующим образом. На передающей стороне передаваемый код анализируется и дополняется контрольным битом до четного или нечетного числа единиц в суммарном коде. Соответственно суммарный код называется четным или нечетным. В случае нечетного кода дополнительный бит формируется таким образом, чтобы сумма всех единиц в передаваемом коде, включая контрольный бит, была нечетной. При контроле четности все, естественно, наоборот. Например, в числе 0111 число единиц нечетно. Поэтому при контроле нечетности дополнительный бит должен быть нулем, а при контроле четности — единицей. На практике чаще всего используется контроль нечетности, поскольку он позволяет фиксировать полное пропадание информации (случай нулевого кода во всех информационных разрядах). На приемной стороне производится проверка кода четности. Если он правильный, то прием разрешается, в противном случае включается сигнализация ошибки или посылается передатчику запрос на повторную передачу.

Схема формирования бита четности для четырехразрядного кода содержит четыре элемента Исключающее ИЛИ, выполняющий функции сумматоров по модулю 2 (без переноса) и состоит из трех ступеней. На первой ступени попарно суммируются все биты исходного кода на входах A, B, C, D. На второй ступени анализируются сигналы первой ступени и устанавливается четность или нечетность суммы входного кода. На третьей ступени полученный результат сравнивается с контрольным сигналом на входе E, задающим вид используемого контроля, в результате чего на выходе F формируется пятый дополнительный бит, четности, сопровождающий информационный сигнал в канале передачи.

## 3.2.5 Контрольные вопросы и задания

- 3.2.5.1 Что такое мультиплексор, каково его назначение?

- 3.2.5.2 Используя методику анализа двухканального мультиплексора с помощью логического преобразователя, исследуйте внутреннюю структуру сдвоенного четырехканального мультиплексора 74153. Из сопоставления обозначений выводов этой ИМС и ее отечественного аналога К155КП2 следует, что их функциональное назначение таково: А, В адресные входы, 10, 20 инверсные входы разрешения первого и второго мультиплексоров, 1С0...1СЗ и 2С0...2СЗ, ІҮ и 2Ү входы и выходы первого и второго мультиплексоров соответственно.

- 3.2.5.3 Что такое демультиплексор, для решения каких задач его можно применить?

- 3.2.5.4 С помощью логического преобразователя, проведите исследования демультиплексора на рисунке 3.4.

- 3.2.5.5 Синтезировать мультиплексор с 5 информационными входами.

- 3.2.5.6 Реализовать функцию из лабораторной №1 задание №7, используя 16-канальный мультиплексор.

- 3.2.5.7 Синтезировать демультиплексор с 3 адресными входами.

- 3.2.5.8 Что такое шифратор, при решении каких задач он используется?

- 3.2.5.9 Синтезировать приоритетный шифратор на 10 входов.

- 3.2.5.10 При решении каких задач цифровой техники используется дешифратор?

- 3.2.5.11 Синтезировать трехразрядный дешифратор на 6 или 5 выходов.

- 3.2.5.12 Какие функции выполняет цифровой компаратор, в каких устройствах он может быть использован?

- 3.2.5.13 Синтезировать двухразрядный цифровой компаратор и проверить его работу.

- 3.2.5.14 Синтезировать четырехразрядный цифровой компаратор и проверить его работу.

- 3.2.5.15 Какое назначение имеют формирователи кода четности, где они могут быть использованы?

- 3.2.5.16 Какая форма контроля четности чаще всего используется на практике, в частности, в Вашем компьютере, если в нем установлены модули ОЗУ с нечетным числом микросхем?

- 3.2.5.17 Синтезировать устройство генерации контрольного разряда для восьмиразрядного кода при контроле на четность.

- 3.2.5.18 Синтезировать устройство генерации контрольного разряда для восьмиразрядного кода при контроле на нечетность.

- 3.2.5.19 Синтезировать устройство контроля восьмибитного числа по нечетности.

- 3.2.5.20 Синтезировать устройство контроля восьмибитного числа по четности.

## 3.3 Лабораторная работа №3

Цель работы: Исследование и синтез сумматоров.

## 3.3.1 Арифметические сумматоры

Арифметические сумматоры являются составной частью так называемых арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти. В программе EWB арифметические сумматоры представлены в библиотеке Comb'I двумя базовыми устройствами, показанными на рисунке 3.5: полусумматором и полным сумматором. Они имеют следующие назначения выводов: А В – входы слагаемых,  $\Sigma$  – результат суммирования. Со – выход переноса, Ci – вход переноса. Многоразрядный сумматор создается на базе одного полусумматора и n полных сумматоров.

Рисунок 3.5 - Схемы полусумматора и полного сумматора

Для исследования внутренней структуры и логики функционирования сумматоров как нельзя лучше подходит логический преобразователь. После подключения полусумматора к преобразователю получаем таблицу истинности и булево выражение. Сравнивая полученные данные с результатами исследования базовых логических элементов в предыдущем разделе, приходим к выводу, что при подключении вывода полусумматора к зажиму ОUТ преобразователя он выполняет функции элемента - Исключающее ИЛИ. Подключив клемму ОUТ преобразователя к выходу Со полусумматора и проделав аналогичные действия приходим к выводу, что в таком включении полусумматор выполняет функции элемента И.

# 3.3.2 Контрольные вопросы и задания

- 3.3.2.1 Чем отличается полусумматор от полного сумматора?

- 3.3.2.2 Установите различия в булевых выражениях и графических обозначениях логических элементов программы EWB от принятых в отечественной научно-технической литературе.

- 3.3.2.3 Синтезировать сумматор (на входе а и b; выход сумма). Нельзя использовать XOR.

- 3.3.2.4 Синтезировать полусумматор (на входе а и b; выход сумма и перенос).

- 3.3.2.5 Синтезировать полный сумматор (на входе a, b и перенос; выход сумма и перенос).

- 3.3.2.6 Синтезировать 4-разрядный параллельный сумматор с параллельным

переносом. Предусмотреть вход переноса.

3.3.2.7 Синтезировать 8-разрядный сумматор с групповым переносом (группа 4 разряда).

## 3.4 Лабораторная работа №4

Цель работы: Изучить принципы работы основных типов триггеров. Научиться синтезировать их и преобразовывать триггеры из одного типа в другой.

## 3.4.1 Исследование триггеров и триггерных схем

Триггерные схемы в программе EWB 4.1 представлены в библиотеке Seg'I тремя типами триггеров RS, JK и D. Назначение выводов триггеров следующее. Для всех триггеров выходы Q – прямой, Q` – инверсный.

Для RS триггера R — установка триггера в 0, при сигнале 1 на этом входе Q=0, Q`=1; S — установка в 1, при сигнале 1 на этом входе Q=1, Q'=0; комбинация R=1, S=1 не изменяет состояния выходов и относится к запрещенным. Для ЈКтриггера Ј,К — информационные входы, > — тактовый вход; вывод сверху — асинхронная предустановка триггера в единичное состояние (Q=1) вне зависимости от состояния сигналов на входах (функционально аналогичен входу S RS-триггера); вывод внизу — асинхронная предустановка триггера в нулевое состояние (так называемая очистка триггера, после которой Q`=1); наличие кружочков на изображениях выводов обозначает, что активными являются сигналы низкого уровня, а для тактового входа — что переключение триггера производится не по переднему фронту тактового импульса, а по его срезу (так чаще всего называют задний фронт импульса). Для D-триггера вход D — информационный, состояние этого входа после подачи тактового импульса запоминается триггером, т.е. при D=1 имеем Q=1, при D=0 Q=0.

Для проведения исследования триггерных схем уже нельзя использовать логический преобразователь, поскольку триггер является элементом памяти. Для этого необходимо подключить к его входам генератора слова и светодиодные индикаторы к выходам. Заметим, что тактовый вход триггера необходимо соединить с выходом синхронизации генератора.

Конечной задачей исследования является получение таблицы истинности, являющейся одной из основных характеристик триггера. Получение ее целесообразно проводить в следующем порядке:

- а) последовательно подать на входы предустановки триггера активные сигналы высокого уровня (сигнал 1) и зафиксировать состояние выхода триггеров для случая предустановки в 1 и 0, для проверки асинхронности этих входов указанные операции повторить при различных состояниях сигналов на тактовом и информационных входах. В дальнейшем на эти входы подавать только сигналы логического нуля;

- б) подать на тактовый и информационные входы сигналы 0 и 1 в различных комбинациях (на входах асинхронной предустановки при этом должны быть сигналы логического нуля для всех комбинаций) и зафиксировать для каждой комбинации состояние выходов триггера;

- в) на основании полученных результатов составить таблицу истинности.

#### 3.4.2 Контрольные вопросы и задания

- 3.4.2.1. Какие типы триггеров Вы знаете, чем обусловлено их многообразие?

- 3.4.2.2. Определите кодовые комбинации на выходе генератора слова для исследования ЈК-триггера в соответствии с описанной методикой. Полученную таблицу истинности сравните с таблицей истинности, вызываемой нажатием клавиши помощи F1 после выделения на схеме триггера.

- 3.4.2.3. Синтезировать триггеры RS,D,T, синхронный JK в базисе И-НЕ и в базисе ИЛИ-НЕ. Для осуществления задержки использовать элемент "буфер". Для всех триггеров обозначить входы и выход Q. (8-схем)

- 3.4.2.4. Преобразовать JK триггер в триггеры RS,D,T. Взяв один из триггеров RS,D,T, преобразовать его в любой из RS,D,T, кроме самого себя. Использовать стандартные триггеры запрещается. На схеме обозначить входы и выходы основного и полученного триггеров. (2-схемы)

- 3.4.2.5. Синтезировать на логических элементах двухступенчатый RS триггер. На схеме обозначить входы и выходы обоих триггеров.

- 3.4.2.6. Синтезировать на логических элементах динамический D-тригер. На схеме обозначить входные, выходные и промежуточные сигналы.

- 3.4.2.7. Проверить работу всех триггеров.

## 3.5 Лабораторная работа №5

Цель работы: Анализ работы и синтез счетчиков и пересчетных устройств.

## 3.5.1 Анализ работы счетчиков и пересчетных устройств

Счетчиком называют устройство, сигналы на выходе которого отображают число импульсов, поступивших на счетный вход. Счетчик, образованный цепочкой из m триггеров, может подсчитать в двоичном коде  $2^m$  импульсов. Каждый из триггеров такой цепочки называют разрядом счетчика. Число m определяет количество разрядов двоичного числа, которое может быть записано в счетчик. Число  $K_{cu}$ = $2^m$  называют коэффициентом (модулем) счета.

Информация снимается с прямых и (или) инверсных выходов всех триггеров. В паузах между входными импульсами триггеры сохраняют свои состояния, т.е. счетчик запоминает число входных импульсов.

Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом. Остальные состояния нумеруются по числу поступивших входных импульсов, Когда число входных импульсов  $N_{\rm Bx} > K_{\rm cq}$  происходит переполнение, после чего счетчик возвращается в нулевое состояние и цикл повторяется. Коэффициент счета, таким образом, характеризует число входных импульсов, необходимое для выполнения одного цикла и возвращения в исходное состояние. Число входных импульсов и состояние счетчика взаимно определены только для первого цикла.

После завершения каждого цикла на выходах последнего триггера возникают перепады напряжения. Это определяет второе назначение счетчиков: деление числа входных импульсов. Если входные сигналы периодичны и следуют с частотой  $F_{\text{вх}}$ , то частота выходных сигналов равна:

$$F_{BHX} = F_{BX}/K_{CY}$$

.

В этом случае коэффициент счета называется коэффициентом деления и обозначается как  $K_{\mbox{\tiny дел}}$  .

У счетчика в режиме деления используется выходной сигнал только последнего триггера, промежуточные состояния остальных триггеров во внимание не принимаются. Всякий счетчик может быть использован как делитель частоты. Поэтому подобное устройство часто называют счетчиком-делителем. Такие делители имеют целочисленный коэффициент деления. Однако элементная база современной микроэлектроники позволяет создавать делители и с дробными коэффициентами деления.

Символом счетчиков на схемах служат буквы СТ (от англ. Counter-счетчик), после символа проставляют число, характеризующее модуль счета (например, 2 или 10–СТ2, СТ10).

Основными эксплуатационными показателями счетчика являются емкость и быстродействие. Емкость счетчика, численно равная коэффициенту счета, равна числу импульсов за один цикл.

Быстродействие счетчика определяется двумя параметрами: разрешающей способностью  $T_{\text{раз.сп}}$  и временем установки кода счетчика  $T_{\text{уст}}$ . Под разрешающей способностью подразумевают минимальное время между двумя входными сигналами, в течение которого не возникают сбои в работе. Обратная величина  $F_{\text{max}} = 1/T_{\text{раз.сп}}$  называется максимальной частотой счета. Время установки кода  $T_{\text{уст}}$  равно времени между моментом поступления входного сигнала и переходом счетчика в новое устойчивое состояние. Эти параметры зависят от быстродействия триггеров и способа их соединения между собой.

Счетчики различаются числом и типами триггеров, способами связей между ними, кодом, организацией счета и другими показателями. Цифровые счетчики классифицируются по следующим параметрам:

- коэффициент счета двоичные (бинарные); двоично-десятичные (декадные) или с другим основанием счета; с произвольным постоянным и переменным (программируемым) коэффициентом счета;

- направление счета суммирующие, вычитающие и реверсивные;

- способ организации внутренних связей с последовательным, параллельным или с комбинированным переносом, кольцевые.

Классификационные признаки независимы и могут встречаться в разных сочетаниях: например, суммирующие счетчики бывают как с последовательным, так и с параллельным переносом, они могут иметь двоичный, десятичный и иной коэффициенты счета.

Введением дополнительных логических связей — обратных и прямых — двоичные счетчики преобразуются в недвоичные. Наибольшее распространение получили десятичные (декадные) счетчики, работающие с  $K_{cq}$ =10 в двоично-десятичном коде (двоичный — по коду счета, десятичный — по числу состояний).

Десятичные счетчики организуются из четырехразрядных двоичных счетчиков. Избыточные шесть состояний исключаются введением дополнительных связей. Возможны два варианта построения схем: счет циклически идет от 0000 до 1001 и исходным состоянием служит 0110B=6D; счет происходит до 1111B=15D, (В, D – обозначения двоичного и десятичного чисел).

Первый вариант на практике применяется чаще.

В суммирующем счетчике каждый входной импульс увеличивает на единицу число, записанное в счетчик, при этом перенос информации из одного разряда в другой, более старший, имеет место, когда происходит смена состояния 1 на 0.

Вычитающий счетчик действует обратным образом: двоичное число, хранящиеся в счетчике, с каждым поступающим импульсом уменьшается на единицу. Переполнение вычитающего счетчика происходит после достижения им нулевого состояния. Перенос из младшего разряда в старший здесь имеет место при смене состояния младшего разряда с 0 на 1.

Реверсивный счетчик может работать в качестве суммирующего и вычитающего. Эти счетчики имеют дополнительные входы для задания направления счета. Режим работы определяется управляющими сигналами на этих входах. В программе EWB такие счетчики представлены ИМС 74163 и 74169 (К155ИЕ18, ИЕ17).

Счетчики с последовательным переносом представляют собой цепочку триггеров, в которой импульсы, подлежащие счету, поступают на вход первого триггера, а сигнал переноса передается последовательно от одного разряда к другому.

Главное достоинство счетчиков с последовательным переносом — простота схемы. Увеличение разрядности осуществляется подключением дополнительных триггеров к выходу последнего триггера. Основной недостаток счетчиков с последовательным переносом — сравнительно низкое быстродействие, поскольку триггеры срабатывают последовательно, один за другим. Счетчики этого класса в библиотеке EWB не представлены.

Максимальная частота счета определяется режимом работы. Если считывание состояния счетчика должно происходить после каждого входного импульса, как это имеет место, например, при счете до заданного числа, то максимальная частота равна:

$$F_{\text{max}} = 1/[(m-1)T_{3\pi\pi} + T_{cp}],$$

где т – число разрядов;

Т<sub>здп</sub> – задержка переключения одного триггера;

Т<sub>ср</sub> – время срабатывания внешнего элемента или считывающей схемы.

Счетные импульсы подаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующим только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, и задержка переключения всего счетчика равна задержке одного триггера. В таких счетчиках используются ЈК- и D-триггеры. В схемном отношении они сложнее счетчиков с последовательным переносом. Число разрядов у этих счетчиков обычно невелико (4...6), поскольку с повышением числа разрядов число внутренних логических связей быстро растет.

Счетчики с параллельным переносом применяются в быстродействующих устройствах. Они обладают более высокой помехоустойчивостью, так как в паузах между импульсами триггеры счетчика блокированы. К их недостаткам

следует отнести меньшую нагрузочную способность отдельных разрядов из-за дополнительной нагрузки внутренними связями. Каскад, предшествующий счетчику, должен иметь достаточную мощность, чтобы управлять входами нескольких триггеров.

Счетчики с параллельным переносом (их чаще называют синхронными) в библиотеке EWB представлены счетчиками 74160, 74162, 74163 и 74169 (аналоги – К155ИЕ9, ИЕ11, ИЕ18, ИЕ17 соответственно).

В счетчике с параллельно-последовательным переносом триггеры объединены в группы так, что отдельные группы образуют счетчики с параллельным переносом, а группы соединяются последовательно. В роли групп могут быть и готовые счетчики. Счетчики этого типа, как правило, многоразрядные. Общий коэффициент счета равен произведению коэффициентов счета всех групп. По быстродействию они занимают промежуточное положение.

Счетчики-делители, оформленные как самостоятельные изделия, имеются в составе многих серий микросхем. Номенклатуру счетчиков отличает большое разнообразие. Многие из них обладают универсальными свойствами и позволяют управлять коэффициентом и направлением счета, вводить до начала цикла исходное число, прекращать счет по команде, наращивать число разрядов и т.п. С помощью готовых счетчиков можно решить большинство практических задач, возникающих перед разработчиком аппаратуры.

В ряде случаев может возникнуть потребность в счетчиках с нетиповыми характеристиками. Они создаются из отдельных триггеров и логических элементов.

Проектирование счетчика сводится к определению числа триггеров и организации связей между ними и логическими элементами, а также вычислению разрешающей способности счетчика (максимальной частоты счета).

На первом шаге проектирования заданный коэффициент счета (деления) преобразуется в двоичный код. Число разрядов двоичного числа показывает, сколько триггеров должен иметь счетчик, а число единиц определяет число входов логического элемента. Входы элемента подключаются к прямым выходам Q тех триггеров, которые соответствуют единицам двоичного числа. Следует только учитывать, что первый, входной триггер отображает младший разряд числа. Выход логического элемента соединяется со входами установки нуля (входы E) всех триггеров, от которых сделаны отводы, а также тех, которые непосредственно за ними следуют.

Результаты проектирования применимы к триггерам разных видов логики, однако реальные схемы при этом могут различаться в деталях. Поскольку принудительная установка в нуль по R-входу у некоторых типов триггеров осуществляется сигналами логического нуля (ТТЛ, ДТЛ), у других — сигналами логической единицы (КМОП), в первом случае должен быть применен логический элемент И-НЕ, во втором — И. Кроме того, в суммирующем счетчике опрокидывание каждого последующего триггера должно происходить тогда, когда сигнал на выходе предыдущего триггера изменяется от 1 к 0, поэтому важен порядок соединения триггеров между собой. Если в счетчике применяются триггеры с прямым управлением (по фронту  $0 \rightarrow 1$ ), их входы присоединяются к инверсным выходам предыдущих. В случае триггеров с инверсным управлением

входы подключают к прямым выходам. Добавив к исходной схеме несколько дополнительных элементов, можно расширить ее возможности — сделать счетчик с самоостановом (одноразового действия) или обеспечить в режиме деления кратковременный импульс на выходе последнего триггера.

Счетчик ИЕ9 – полностью программируемый, поскольку на каждом из его установить требуемый логический уровень. предварительная установка происходит синхронно с перепадом тактового импульса и не зависит от того, какой уровень присутствует на входах разрешения счета СЕР (ENP) и СЕТ (ENT). Напряжение низкого уровня, поступившее на вход загрузки PE (LOAD'), останавливает счет подготовленным на входах D0...D3 (A, B, C, D) данным загрузиться в счетчик в момент прихода следующего положительного перепада тактового импульса (от низкого к высокому уровню или при переходе от 0 к 1).

Сброс счетчика ИЕ9 — асинхронный. Если на общий вход сброса R поступило напряжение низкого уровня, на выходах всех четырех триггеров устанавливаются низкие уровни независимо от сигналов на входах С (СLК), РЕ, СЕТ и СЕР. Внутренняя схема ускоренного переноса необходима для синхронизации многодекадной цепи счетчиков ИЕ9. Специально для синхронного каскадирования микросхема имеет два входа разрешения: СЕР (параллельный) и СЕТ (вспомогательный, с условным названием "трюковый"), а также выход ТС (RCD— окончание счета).

Счетчик считает тактовые импульсы, если на обоих его входах СЕР и СЕТ напряжение высокого уровня. Вход СЕТ последующего счетчика получает разрешение счета в виде напряжения высокого уровня от выхода ТС предыдущего счетчика. Длительность высоких уровней (сигнала логической 1) на выходе ТС примерно соответствует длительности высокого уровня на выходе Q0 предыдущего счетчика.

Для счетчиков ИЕ9 не допускаются перепады от высокого уровня к низкому на входах СЕР и СЕТ, если на тактовом входе присутствует напряжение низкого уровня. Нельзя подавать положительный перепад на вход РЕ, если на тактовом входе присутствует напряжение низкого уровня, а на входах СЕР и СЕТ – высокого (во время перепада или перед ним). Сигналы на входах СЕР и СЕТ можно изменять, если на тактовом входе С присутствует напряжение низкого уровня. Когда на входе РЕ появляется высокий уровень, а входы СЕ неактивны (т.е. на СЕР и СЕТ – низкий уровень), то вместе с последующим положительным перепадом тактового импульса на выходах Q0,..Q3 (QA, QB, QC, QD) появится код от входов D0...D3.

Подавая сигналы высокого уровня на входы СЕТ и СЕР при низком уровне сигнала на тактовом входе, получим на выходах наложение кодов загрузки и внутреннего счета. Если при низком уровне тактового сигнала на входы СЕТ, СЕР и РЕ поданы положительные перепады, нарастающие от низкого уровня к высокому, тактовый перепад изменит код на выходах Q1...Q3 на последующий.

При входных сигналах высокого уровня счетчик К155ИЕ9 (74160) потребляет ток питания 94 мА, К555ИЕ9 (74LS160A) – 32 мА; если все выходные сигналы имеют низкий уровень, то 101 и 32 мА соответственно. Максимальная частота счета 25 МГц. Время распространения сигнала от входа С до выхода ТС ("Счет закончен") составляет 35 и 27 не, а время сброса (от входа R до выходов Q)

38 и 28 нс для обычного исполнения и варианта Шотки.

## 3.5.2 Контрольные вопросы и задания

- 3.5.2.1 Что такое счетчик, какого типа они бывают?

- 3.5.2.2 Как образом создаются счетчики с коэффициентом счета, не кратным 2?

- 3.5.2.3 Что такое программируемый счетчик?

- 3.5.2.4 Исследовать работы счетчиков К155ИЕ9, ИЕ11; К155ИЕ17,ИЕ18

- 3.5.2.5 Синтезировать 4-разрядный суммирующий счетчик на ЈК-тригерах.

- 3.5.2.6 Синтезировать 4-разрядный вычитающий счетчик на ЈК-тригерах.

- 3.5.2.7 Синтезировать на D-тригерах 3-разрядный синхронный суммирующий счетчик с логикой формирования переноса и входом разрешения счета. Соединить 3 полученных счетчика для увеличения разрядности счета до 9.

- 3.5.2.8 Синтезировать счетчик с изменяемым направлением счета. 3-разрядный.

- 3.5.2.9 Синтезировать 3-разрядный счетчик с предварительной установкой, сбросом, логикой формирования переноса. Предусмотреть вход разрешения (запрещения) работы счетчика. Счетчик в выключенном состоянии не должен реагировать на сигналы синхроимпульса и загрузки.

- 3.5.2.10 Синтезировать 4-разрядный счетчик, который при одном состоянии управляющего сигнала считает от 0 до 9, а при другом по коду Грея. В отчете показать полный синтез этого счетчика.

## 3.6 Лабораторная работа №6

Цель работы: Исследовать и синтезировать устройства хранения и преобразования данных.

# 3.6.1 Анализ функционирования регистров

Основное назначение хранение преобразование регистров И чисел. счетчиками многоразрядных Регистры двоичных наряду co запоминающими устройствами являются наиболее распространенными устройствами цифровой техники. При сравнительной простоте регистры обладают большими функциональными возможностями. Они используются в управляющих устройств, генераторов качестве И запоминающих преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки. Элементами структуры регистров являются синхронные триггеры Dили ЈК-типа с динамическим или статическим управлением. Одиночный триггер может запоминать (регистрировать) один разряд (бит) двоичной информации. Такой триггер можно считать одноразрядным регистром. Занесение информации в регистр называют операцией ввода или записи. Выдача информации к внешним устройствам характеризует операцию вывода считывания. или информации в регистр не требует его предварительного обнуления.

Понятие "весовой коэффициент" к разрядам регистра в отличие от счетчика неприменимо, поскольку весовая зависимость между отдельными разрядами целиком определяется записанной в регистр информацией. По этой причине на

условных изображениях регистров нумерация информационных входов и выходов наносится подряд.

Все регистры в зависимости от функциональных свойств подразделяются на две категории – накопительные (регистры памяти, хранения) и сдвигающие. В свою очередь, сдвигающие регистры делятся по способу ввода и вывода информации на параллельные, последовательные И комбинированные (параллельно-последовательные последовательно-параллельные), направлению передачи (сдвига) информации – на однонаправленные И реверсивные.

Наиболее простыми регистрами являются регистры памяти. Их назначение—хранение двоичной информации небольшого объема в течение короткого промежутка времени. Эти регистры представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись) и вывод (считывание) информации производится параллельным кодом. Ввод обеспечивается тактовым импульсом, с приходом очередного тактового импульса записанная информация обновляется. Считывание производится в прямом или в обратном коде (в последнем случае с инверсных выходов).

Регистры хранения представляют собой наборы триггеров с независимыми информационными входами и обычно общим тактовым входом. В таком качестве используются синхронные триггеры, составленные из микросхем, содержащих в одном корпусе несколько самостоятельных триггеров, например К155ТМ8 (74175), К155ТМ9 (74179) и другие, которые можно рассматривать как 4—6-разрядные регистры памяти. Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров, тактовые входы которых подсоединяют к шине синхронизации.

Вторым наиболее распространенным классом регистров являются регистры сдвига, которые отличаются большим разнообразием как в функциональном отношении, так и в отношении схемных решений и характеристик. Регистры осуществляют преобразование хранения, сдвига, помимо операции последовательного двоичного кода в параллельный, а параллельного - в последовательный, выполняют арифметические и логические операции, служат в качестве элементов временной задержки. Своим названием они обязаны характерной для этих устройств операции сдвига. С приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования единиц и нулей. При сдвиге информации вправо после каждого тактового импульса бит из более старшего разряда сдвигается в младший, а при сдвиге влево – наоборот.

На отечественных схемах символом регистра служат буквы RG. Для регистров сдвига указывается также направление сдвига: > – вправо; < – влево; <-> – реверсивный (двунаправленный).

## 3.6.2 Контрольные вопросы и задания

- 3.6.2.1 Что такое регистр, какие функции он может выполнять?

- 3.6.2.2 Назовите типы регистров и их возможные применения.

- 3.6.2.3 Исследовать работу нескольких регистров имеющихся в библиотеке.

- 3.6.2.4 Синтезировать параллельный 8-разрядный регистр.

- 3.6.2.5 Синтезировать последовательный 4-разрядный регистр на RS триггерах.

- 3.6.2.6 Синтезировать параллельно последовательный 4-разрядный регистр на ЈК триггерах.

- 3.6.2.7 Синтезировать реверсивный 4-разрядный регистр сдвига на D триггерах.

- 3.6.2.8 Для всех регистров предусмотреть вход сброса.

# Список использованных источников

- 1. Карлащук В.И. Электронная лаборатория на IBM PC. Программа Electronics Workbench и её применение. М.: Солон-Р, 1999 506с.

- 2. Забродин Ю.С. Промышленная электроника. М.: Высшая школа, 1982. 496с.

- ЛачинВ.И., Савёлов Н.С., Электроника. Ростов н/Д.: Феника, 2000 448с.

- 4. Васильев В.И., Гусев Ю.М., Миронов В.Н. Электронные промышленные устройства. М.: Высшая школа, 1988. 303с.

- 5. Розанов Ю.К. Основы силовой электроники. М.: Энергоатомиздат, 1992.- 296с.